←

Pipelined ISA CPU (Verilog)

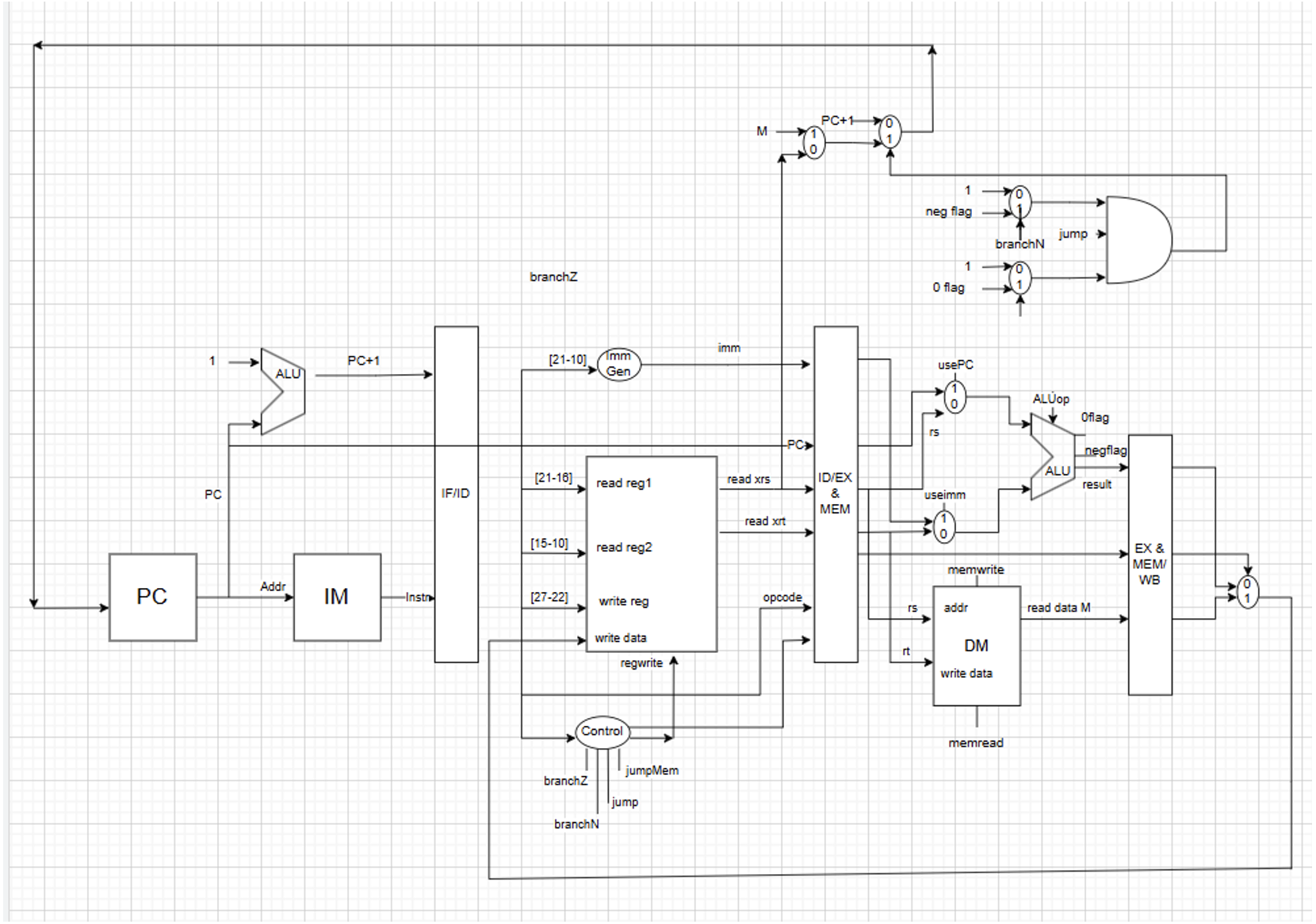

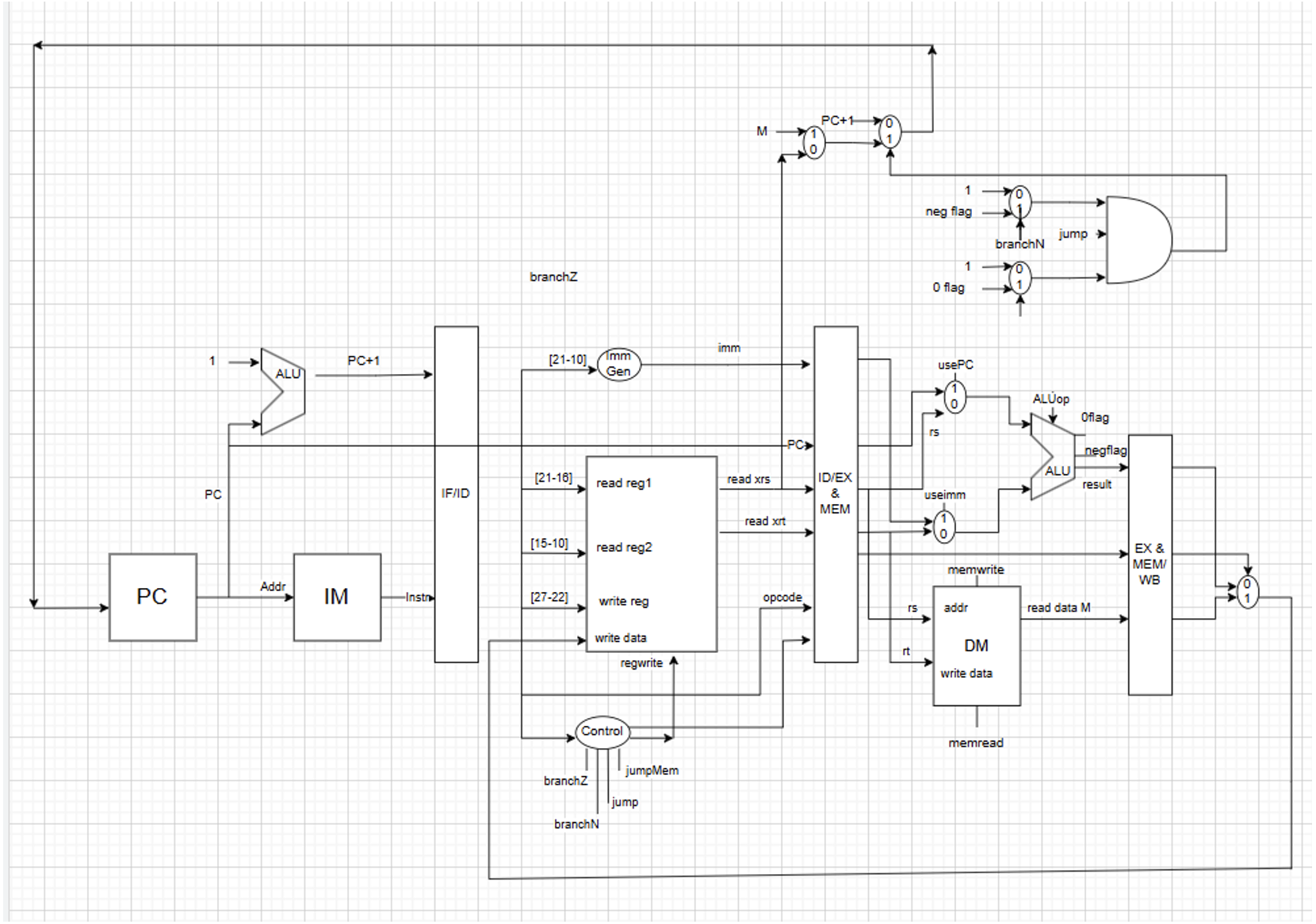

This 5-stage pipelined CPU was implemented in Verilog HDL based on the SCU ISA, with support for 12 instructions including arithmetic, memory, and control flow operations. Instructions follow a fixed 32-bit format, and the pipeline includes IF, ID, EX, MEM, and WB stages with hazard-handling logic.

The CPU was tested with assembly programs like a MIN function and vector addition. Control signals are managed via a centralized unit with a truth table, and data/control flow is verified through waveform simulation. The pipeline achieves one-instruction-per-cycle throughput in ideal cases, with performance analysis estimating a base CPI of ~1.5 and max clock frequency of 250 MHz.

Project LinkThe CPU was tested with assembly programs like a MIN function and vector addition. Control signals are managed via a centralized unit with a truth table, and data/control flow is verified through waveform simulation. The pipeline achieves one-instruction-per-cycle throughput in ideal cases, with performance analysis estimating a base CPI of ~1.5 and max clock frequency of 250 MHz.